# Investigation of the effects of different thin film deposition parameters on electronic parameters of In<sub>2</sub>S<sub>3</sub>/n-InP junctions at various temperatures

# Tuba Çakıcı

Department of Physics, Science Faculty, Atatürk University, Erzurum, Turkey

# Mustafa Sağlam

Department of Physics, Science Faculty, Atatürk University, Erzurum, Turkey

#### **ABSTRACT**

In this research, we report on the measurement of the current-voltage (I-V) capacitance-voltage (C-V) characteristics two different  $Au/In_2S_3/n-InP/In$  Schottky diodes at various temperatures and in dark condition fabricated by chemically spray pyrolysis process. For this, we initially made ohmic contacts on two pieces n-InP crystals with In metal. Then  $In_2S_3$  thin films, which are changed deposition parameters, have been directly grown on n-InP substrates by using chemically spray pyrolysis method (SPM). The morphology, topology and elemental analysis of  $In_2S_3$  thin films that is grown different parameters, examined with AFM, SEM and EDX techniques. Then, Au contact metal evaporated on the  $In_2S_3$  thin films, having two different film deposition parameters. Some temperature dependent electronic parameters of two different  $In_2S_3/n$ -InP junctions extracted to I-V-T and C-V-T curves.

**Keywords:** In<sub>2</sub>S<sub>3</sub>; Spray Pyrolysis Method; I-V-T; C-V-T;

#### 1 INTRODUCTION

The barrier height (BH) is likely to be a function of the interface atomic structure and the atomic inhomogeneities at the metal— semiconductor (MS) interface which are caused by grain boundaries, multiple phases, facets, defects, a mixture of different phases etc.[1-2]. Also Interfacial properties M-S contacts have a dominant influence on the device performance, reliability and stability.

Indium phosphide is one of the most important semiconductors being considered for device applications, especially is promising material for high-speed electronic and optoelectronic devices, however their implementation is somewhat hampered by difficulties in reproducibly controlling their surface composition and electrical properties. These difficulties are caused by interface instability and surface recombination velocity [3]. Used the thin film modifies some electrical characteristics of the diodes. Because of the suitability and stability of the  $In_2S_3$  thin film, it is used in barrier modification of metal—n type InP semiconductor devices [1,4-5]. In the literature Wilmsen and co-workers suggested that S fills the phosphorous vacancies and replaces the surface P with sulfur. It was suggested that an  $In_2S_3$  -InP heterojunction structure may be formed as a result of the S treatment. The proposed arrangement of S leaves the passivated surface with no dangling bonds [6].

In our previous article, two different  $In_2S_3$  /n-InP junctions have been fabricated by SPM and the effects of the growing parameters  $In_2S_3$  interlayer on electrical characteristics of  $In_2S_3$  /n-InP junctions have been examined at room temperature [4]. In this work, characteristics of the same two different junctions'

temperature depend I-V-T and C-V-T have been investigated over the temperature range 300-20 K with steps in 40 K.

#### 2 EXPERIMENTAL METHOD

Firstly, two pieces n-InP (1 0 0) crystals were degreased consecutively in trichloroethylene, acetone, and methanol for 5 min then rinsed in deionized water of 18 M $\Omega$ . The native oxide on the surfaces were etched in sequence with acid solutions (H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O=3:1:1) for 1 min. Then a blow-dry with N<sub>2</sub>, ohmic contacts on the back side of the samples were formed by evaporating indium metal at a pressure of about  $10^{-5}$  Torr, followed by annealing at 320°C for 3 min in N<sub>2</sub> atmosphere.

Then as shown in Table 1, the  $In_2S_3$  thin films which have different growing parameters ,were directly deposited on the surfaces of n-InP semiconductors with In ohmic contacts by spray pyrolysis method to investigate thin films growing effects on the electrical characteristics at various temperatures. The detailed structural and morphology properties of the  $In_2S_3$  thin films on n-InP substrates were investigated with AFM, SEM and EDX techniques. We were shown the same experimental steps of deposited the  $In_2S_3$  thin films in our previous article [4].

| Substrate | prec | ity of the<br>cursors<br>ons (M)<br>(NH <sub>2</sub> ) <sub>2</sub><br>CS | Molar<br>ratio of<br>precursors<br>solutions<br>(In/S) | Substrate<br>Temperatu<br>re ( <sup>0</sup> C) | Carrier<br>gas | Flow<br>Rate/Flow<br>Factor | Total<br>sprayed | Film<br>Growth<br>Process<br>time<br>(min) |

|-----------|------|---------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------|----------------|-----------------------------|------------------|--------------------------------------------|

| n-InP/In  | 0,01 | 0,01                                                                      | 2/3                                                    | 300                                            | Air            | 6/5                         | 100 ml           | 20                                         |

| n-InP/In  | 0,01 | 0,01                                                                      | 2/3                                                    | 300                                            | Air            | 6/5                         | 200 ml           | 40                                         |

Table 1 The growing parameters of In<sub>2</sub>S<sub>3</sub> thin film on n-InP substrates by Spray pyrolysis method

Finally, Au metal contacts were evaporated on the  $In_2S_3$  thin films, having different growing parameters and two different junctions ( $Au/In_2S_3/n$ -InP/In) were obtained. The reverse and forward bias I-V-T measurements were examined by the use of a Keithley 2400 source meter in the temperature range of 300-20 K by steps of 40 K under dark conditions using a temperature-controlled Leybold Heraeus closedcycle helium cryostat. The sample temperature was always monitored by using a Lake Shore model 321 auto tuning temperature controllers with sensitivity. Also, in order to examine C-V-T characteristics of device in the temperature range of 300-20 K by steps of 40 K under dark conditions was used HP model 4192A LF impedance analyzer with temperature-controlled Leybold Heraeus closed-cycle helium cryostat. This experimental measerements systems are shown in Figure 1.

Figure 1The experimental setup where the I-V-T and C-V-T measurements

# 3 RESULTS AND DISCUSSION

# 3.1 Analysis of the $In_2S_3$ thin films

It can be said that the interfacial features and roughness of the interlayer thin film plays significant role in determining the properties of any metal-interlayer thin film-semiconductor device, as the metal-semiconductor interface strongly affects transport across a junction. We were shown AFM, SEM, and EDX the detail analysis of the  $In_2S_3$  thin films in our previous article [4].

## 3.2 Electrical characteristics of two different In<sub>2</sub>S<sub>3</sub> /n-InP junctions at various temperatures

#### 3.2.1. Temperature dependent I-V-T.

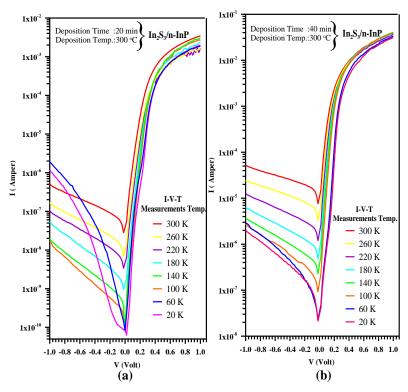

Figure 2 a and b show the semi-logarithmic forward-reverse bias I-V characteristics of two different  $Au/In_2S_3/n-InP/In$  structure as a function of sample temperature. According to the thermionic emission theory, it is assumed that the forward bias current of the diodes is due to the thermionic emission current and can be expressed as

$$I = AJ = \left\{ AA^*T^2 exp\left(\frac{-q\Phi_{B0}}{kT}\right) \right\} \left\{ exp\left(\frac{q(V - IR_S)}{nkT}\right) - 1 \right\}$$

(1)

Where A is the effective area of diode;  $A^*$  is the effective Richardson constant;  $\Phi_{B0}$  is the effective barrier height; T is the temperature; q is the elementary charge; k is Boltzmann constant;  $R_S$  is the series resistance; n is the ideality factor and V is the applied voltage dropped on the Schottky junction. n has usually a value greater than unity. High values of n can be attributed to the presence of the interfacial thin layer and a wide distribution of low-Schottky barrier height patches (or barrier inhomogeneities). The saturation current  $I_0$  denoted by

$$I_0 = AA^*T^2 exp\left(\frac{-q\Phi_{B0}}{kT}\right) \tag{2}$$

is obtained by extrapolation of the forward or reverse bias current–voltage curve to zero applied voltage. It can be seen that the I-V-T plots shift towards the slightly higher bias side with decreasing temperature. From Eq. (1), the ideality factor n can be written as:

$$n = \frac{q}{kT} \frac{dV}{d \left( \ln I \right)} \tag{3}$$

The  $\Phi_{B0}$  was calculated using theoretical value A\* (9.8 A/cm<sup>2</sup> K<sup>2</sup>) and extrapolated I<sub>0</sub> at each temperature according to [6-7]:

$$\Phi_{B0} = (kT/q) \ln \left( \frac{AA^*T^2}{I_0} \right) \tag{4}$$

Fig. 2 shows the semi-logarithmic forward and reverse bias I-V characteristics of  $In_2S_3/n$ -InP structure as a function of sample temperature. Fig. 2 (a) is represented that the junction has the thin film deposition time 20 min, Fig. 2 (b) is represented that the junction has thin film deposition time 40 min as well. Also from these curves, it is obtained n,  $I_0$  (A) and  $\Phi_B$  (eV) values for each junction by using equations of Eqs. 2, 3 and 4. These values are shown in Table 2 and Table 3 for the junctions which have the thin film deposition time 20 min and 40 min respectively.

It is observed that though deposition time 20 min junction of the revers bias current has not reached saturation at lower than 100 K temperature values, it isn't observed such a situation for the other junction. Thus, It can be said that the I-V-T characteristic of the junction, has thin film deposition time 40 min, is more stable to decreasing temperatures.

Table 2 Some parametric values obtained from I-V-T measurements  $In_2S_3/n$ -InPJunction, having 20 min thin film deposition time

| Sample-Temperature (°C) | n      | $\Phi_{\rm B}({ m eV})$ | $I_0(A)$  |

|-------------------------|--------|-------------------------|-----------|

| 300                     | 1.094  | 0.670                   | 4.225E-8  |

| 260                     | 1.190  | 0.620                   | 5.181E-9  |

| 220                     | 1.373  | 0.540                   | 1.758E-9  |

| 180                     | 1.478  | 0.464                   | 2.528E-10 |

| 140                     | 1.970  | 0.346                   | 5.312E-10 |

| 100                     | 2.585  | 0.249                   | 2.116E-10 |

| 60                      | 5.572  | 0.137                   | 8.989E-10 |

| 20                      | 11.640 | 0.047                   | 5.238E-11 |

Table 3 Some parametric values obtained from I-V-T measurements  $In_2S_3/n$ -InPJunction, having 40 min thin film deposition time

| Sample-Temperature (°C) | n      | $\Phi_{\rm B}({ m eV})$ | $I_0(A)$ |

|-------------------------|--------|-------------------------|----------|

| 300                     | 1.080  | 0.530                   | 1.309E-5 |

| 260                     | 1.103  | 0.620                   | 1.959E-6 |

| 220                     | 1.140  | 0.540                   | 3.412E-7 |

| 180                     | 1.369  | 0.464                   | 5.931E-9 |

| 140                     | 1.880  | 0.266                   | 4.082E-7 |

| 100                     | 2.438  | 0.193                   | 1.393E-7 |

| 60                      | 4.023  | 0.129                   | 7.443E-9 |

| 20                      | 11.868 | 0.040                   | 3.151E-9 |

Figure 2: The semi-log forward-reverse bias current-voltage characteristics of two different In<sub>2</sub>S<sub>3</sub>/n-InP junctions at various temperatures. (a) deposition time 20 min and (b) deposition time 40 min.

# 3.2.2. Temperature dependent C-V-T.

For Schottky barrier diode fabricated on an n-type semiconductor, the depletion layer capacitance can be expressed as [4]:

$$\frac{1}{C^2} = \frac{2\left(V_{bi} - V_r - \frac{kT}{q}\right)}{qA^2N_D\varepsilon_0\varepsilon_s} \tag{5}$$

where  $V_{bi}$  is the built-in voltage determined from the extrapolation of the  $C^{-2}$  vs. V plot to the voltage axis,  $V_r$  is the reverse voltage, A is the area of the diode,  $\varepsilon_s$  is the static dielectric constant equal to 12.4 for n-InP,  $\varepsilon_o = 8.85 \times 10^{-14}$  F/cm and  $N_D$  is the concentration of the non-compensated ionized donors. The  $N_D$  is related to the slope of  $C^{-2}$  vs. V curve and can be obtained from the expression given below:

$$N_D = -\frac{2}{q\varepsilon_s\varepsilon_0 A^2} \left[ \frac{d}{dV} \left( \frac{1}{C^2} \right) \right]^{-1} \tag{6}$$

The BH deduced from capacitance is then obtained from:

$$\Phi_B(CV) = V_{bi} + \frac{kT}{q} + \frac{\bar{k}T}{q} \ln(N_C/N_D)$$

(7)

$$\Phi_B(CV) = V_D + \frac{kT}{q} \ln(N_C/N_D)$$

(8)

where  $V_D$  is expressed to as the diffusion potential and  $N_C$  (=5.7 ×10<sup>17</sup> cm<sup>-3</sup>) is the effective density of states in the conduction band for n-InP at 300 K.  $\frac{kT}{q} \ln(N_C/N_D)$  is Fermi level and the bottom of the conduction band.

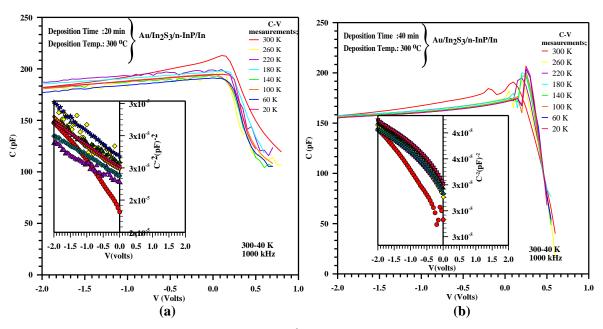

It's seen that temperature depend C-V characteristics parameters, obtained by using Eqs.(6), (7) and (8) of the two for the different junctions at various temperatures. The experimental reverse and forward bias C-V and  $C^{-2}$ -V characteristics of the Au/In<sub>2</sub>S<sub>3</sub>/n-InP/In junctions which have thin film deposition time 20 min and 40 min over the temperature range 300-20 K in steps of 40 K at frequency 1000 kHz are shown in Figs. 3 (a) and (b), respectively.

For the junction that has thin film deposition time 20 min in Fig. 3 (a), the values of barrier heights, the non-compensated concentrations of ionized donor atoms and Fermi level values calculated from  $C^{-2}$ –V characteristics are obtained in the range of 0.800-1.053 eV, in the range of  $4.289 \times 10^{16}$ – $1.980 \times 10^{16}$  cm<sup>-3</sup> and in the range of 0.07-0.002 eV over the temperature range 300-20 K in steps of 40 K at frequency 1000 kHz, respectively

Furthermore, the junction that has thin film deposition time 40 min in Fig. 3 (b), the values of barrier heights, the non-compensated concentrations of ionized donor atoms and Fermi level values calculated from  $C^{-2}$ –V characteristics are obtained in the range of 0.773–1.020 eV, in the range of 4.601  $\times$  10<sup>16</sup>–2.605  $\times$  10<sup>16</sup> cm<sup>-3</sup> and in the range of 0.065-0.003 eV over the temperature range 300-20 K in steps of 40 K at frequency 1000 kHz, respectively.

Figure 3: The reverse and forward bias C-V and C<sup>-2</sup>-V characteristics of two different  $In_2S_3/n$ -InP junctions at various temperatures. (a) deposition time 20 min and (b) deposition time 40 min (f=1000 kHz).

## 4 CONCLUSION

In this study, we prepared the  $In_2S_3$ /n-InP two different junctions and investigated comparative the electrical characteristics of these two different junctions with I–V-T and C–V-T measurements over the temperature range 300-20K with steps in 40 K. For each junction, it is observed that ideality factor increased and the barrier height decreased with the decreased temperature. From the C-V measurement of two different junctions,  $\Phi_B$  (CV), donor concentration ( $N_D$ ), Fermi level ( $E_F$ ) and diffusion potential ( $V_D$ ) have been calculated and compared at 1000 kHz applied frequency at various temperatures. According to the our observations, we reported that both I-V-T and C-V-T characteristic of the junction, has thin film deposition time 40 min, is more stable to decreasing temperatures than the other. Also we say that used as the interfacial layer of the  $In_2S_3$  thin films properties are significantly affect  $In_2S_3$ /n-InP junctions' electrical characteristics and performance.

## REFERENCES

- [1] Çakıcı T., Sağlam M. and Güzeldir B. (2014). Materials Science in Semiconductor Processing, 28, 121–126.

- [2] Asubay S., Gullu O. and Turut A. (2008). Applied Surface Science, 254, 3558–3561.

- [3] Ajayan J. and Nirmal D. (2015). Superlattices and Microstructures, 86, 1–19.

- [4] Çakıcı T. and Sağlam M. (2015). Materials Today: Proceedings, 10.1016/j.matpr.2016.03.069 (Preprint)

- [5] Çakıcı T., Sağlam M. and Güzeldir B, (2015). Materials Science and Engineering B, 193, 61–69.

- [6] Holloway P.H. and Mc Guire G.E. (1995). Handbook Of Compound Semiconductors Growth,

Processing, Characterization, and Devices.

- [7] Çakıcı T., Güzeldir B. and Sağlam M. (2015) Journal of Alloys and Compounds, 646, 954-965.

- [8] Bolognesi A., Carlo A. D., Lugli P., Kampen Y., Zahn D. R. T. (2003) Journal of Physics Condens Matter 15, 2719